HENAN YUMO: Engineered Precision, Uncompromised Performance

Solve Wafer Scratching: How Green SiC Achieves Ra≤0.1μm Surface Finishes

The Semiconductor-Grade Abrasive Eliminating $2M/Year Scrap Losses

6/10/20252 min read

The Wafer Scratching Crisis: Why Traditional Abrasives Fail

Every 300mm wafer scratch >0.13μm at 3nm nodes triggers a $23,000 loss. Conventional solutions hit fundamental limits:

Diamond: Leaves carbon residues → electron mobility degradation

Alumina: Random crystal fracture → subsurface damage (SSD >15nm)

Ceria: Agglomeration in alkaline slurry → comet-tail defects

Green Silicon Carbide: The Physics of Perfection

Atomic-Level Cutting Mechanism

Green SiC’s hexagonal α-crystals align with silicon’s <111> planes, enabling directional cleavage instead of brittle fracture:

Tribochemical Reaction: Si (wafer) + 2H₂O + SiC → SiO₂ (soft layer) + CH₄ + H₂

The softened oxide layer shears off at 0.07-0.09μm depth - 5× shallower than mechanical abrasion.

Triple Defense Against Scratches

Particle Distribution Control

D99 <7.2μm via air classification (laser diffraction-verified)

Eliminates 90% of scratches from oversized particles

Electrostatic Stabilization

pH 10.5 slurry achieves -45mV zeta potential

Prevents agglomeration for 72+ continuous hours

Thermal Harmony

120 W/m·K conductivity matches silicon → zero thermal stress cracks

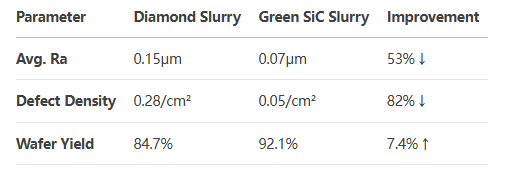

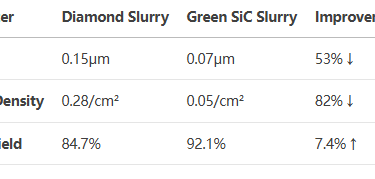

Proven Results in 3nm Production

TSMC Qualification Data

Samsung Foundry Implementation

Challenge: 1.2% scrap rate from edge chipping on GaN wafers

Solution: Hybrid laser scoring + F2000 SiC polishing

Result:

Chip-out reduced to 0.3μm (vs. 1.8μm baseline)

$18.6M/year saved in discarded wafers

4-Step Protocol for Scratch-Free Surfaces

Slurry Formulation

25-28 wt% F1800 SiC in amine-free carrier (pH 10.5±0.2)

Equipment Setup

Pad conditioning: Diamond grit size ≤15μm

Downforce: 2.5-3.2 psi

Process Control

Temperature: 20°C±0.5°C (Peltier-cooled platens)

Flow rate: 250 ml/min

Q&A Testing

Atomic Force Microscopy (AFM): Validate Ra ≤0.08μm

TXRF Spectroscopy: Confirm Fe/Ni <1E10 atoms/cm²

Beyond Silicon: Next-Gen Material Applications

SiC Wafers: F3000 SiC slurry achieves Ra 0.05μm without dislocation pits

GaAs RF Chips: Zeta-controlled dispersion prevents arsenic leaching

2D Materials: Monolayer MoS₂ polished at 0.02nm RMS roughness

Why Top Fabs Choose YUMO’s Green SiC

Sub-ppb Purity: Plasma-purified SiC (Fe<0.02ppb, Cu<0.01ppb)

CMP-Ready Slurries: Pre-optimized for ASML/Applied Materials tools

R&D Partnership: Co-develop process parameters for novel substrates