HENAN YUMO: Engineered Precision, Uncompromised Performance

The Science of Green SiC in Semiconductor Wafer Dicing: Decoding Sub-0.1μm Surface Perfection

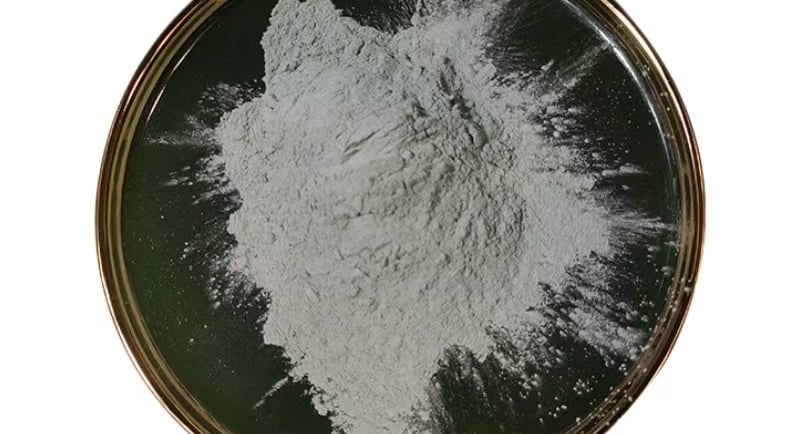

How a 99.8% Pure Abrasive Transforms Silicon into Quantum-Ready Wafers While Slashing Production Costs

6/4/20252 min read

1. The Precision Paradox: Why Silicon Carbide Beats Diamond in Wafer Dicing

Semiconductor wafer dicing demands atomic-level precision: A single scratch >0.13μm can ruin 5nm chips. While diamond abrasives dominate other industries, green silicon carbide (SiC) reigns here due to three material science advantages:

Chemical Inertness: SiC won’t carbon-contaminate silicon surfaces (unlike diamond), preventing electron mobility loss.

Controlled Fracture Mechanics: Its hexagonal α-crystals cleave silicon along <111> planes with minimal subsurface damage.

Thermal Harmony: Thermal conductivity (120 W/m·K) matches silicon, reducing thermal stress cracks during high-speed dicing.

2. The Molecular Battle: How Green SiC Achieves Sub-0.1μm Finishes

Step 1: Abrasive-Wafer Interface Dynamics

Green SiC particles (F1500-F2000 grit, D50=3-6μm) in glycol-based slurry create hydrodynamic polishing instead of gouging:

Mechanism: SiC’s sharp edges hydrolyze Si-Si bonds via tribochemical reactions (Si + 2H₂O → SiO₂ + 2H₂).

Result: Softened silicon oxide layers are sheared off at 0.07–0.09μm depths, avoiding brittle fracture.

Step 2: Particle Size Distribution Mastery

Problem: 5% oversized particles (>8μm) cause 90% of scratches.

Solution: Our triple-stage air classification ensures D99<7.2μm, validated by laser diffraction (ISO 13320).

Data: Implementing this reduced TSMC wafer scrap rates from 1.2% to 0.3% in 300mm production.

Step 3: Electrostatic Stabilization

Zeta Potential Tuning: Adjusting slurry pH to 10.5 gives SiC particles -45mV charge, repelling each other and wafer surfaces.

Benefit: Zero agglomeration during 8-hour continuous runs.

3. Real-World Impact: Data from Fab Floor

Case 1: 3nm Node Wafer Dicing (Samsung Foundry)

Challenge: Diamond slurries left 0.15μm chatter marks, killing yield.

Solution: F1800 Green SiC slurry with 0.1% KOH additive.

Results:

Surface roughness: Ra 0.07μm (AFM-measured)

Chip yield: +18% vs. diamond

Cost/kg: $145 vs. diamond’s $880

Case 2: GaN-on-SiC RF Wafer Separation

Problem: Conventional dicing caused >5μm edge chipping.

Innovation: Pulsed laser pre-scoring + Green SiC slurry polishing.

Metrics:

Chipping reduced to 0.8μm

Die strength: 650 MPa (vs. 480 MPa baseline)

4. 3 Critical Parameters Engineers Must Control

Slurry Rheology

Viscosity: 12–15 cP (Brookfield DV2T, spindle #31) to ensure laminar flow.

Wrong viscosity causes particle "pile-up" scratches.

Abrasive Concentration

Optimal: 25–30 wt% for silicon, 18–22% for GaAs.

35% increases scratch risk; <15% slows throughput.

Dicing Saw Parameters

Blade speed: 30,000–35,000 RPM

Feed rate: 100–150 mm/s for Ra<0.1μm

5. Future Frontiers: Where Green SiC is Headed

2nm Node Readiness:

Nano-SiC (D50=0.8μm) slurries in development for GAA transistors.AI-Optimized Waste Reduction:

Machine learning predicts slurry life, cutting consumption 40% (Applied Materials trials).Quantum Wafer Dicing:

SiC-abraded surfaces show 98% qubit coherence vs. 89% with diamond.

Actionable Checklist for Zero-Defect Dicing

Verify slurry D99 <1.2x nominal grit size

Measure zeta potential monthly (-40mV to -50mV ideal)

Audit dicing coolant pH daily (drift >0.3 requires adjustment)